$V_{\rm S}$

$R_{ON}$

$I_{D(NOM)}$

$V_{\rm DS(AZ) max}$

4.5 - 5.5

60

1

3

0.32

V

V

Ω

A

A

# Smart Quad Low-Side Switch

### Features

- Short Circuit Protection

- Overtemperature Protection

- Overvoltage Protection

8 bit Serial Data Input and Div

- 8 bit Serial Data Input and Diagnostic Output (SPI protocol)

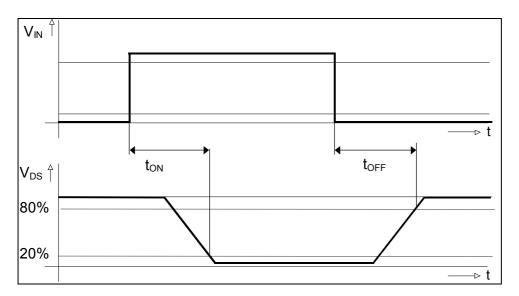

- Direct Parallel Control of Four Channels for PWM Applications

- Cascadable with Other Quad Switches

- Low Quiescent Current

- µC Compatible Input

- Electostatic Discharge (ESD) Protection

### Application

- $\mu C$  Compatible Power Switch for 12 V and 24 V Applications

- Switch for Automotive and Industrial System

- Solenoids, Relays and Resistive Loads

- Injectors

- Robotic controls

### **General Description**

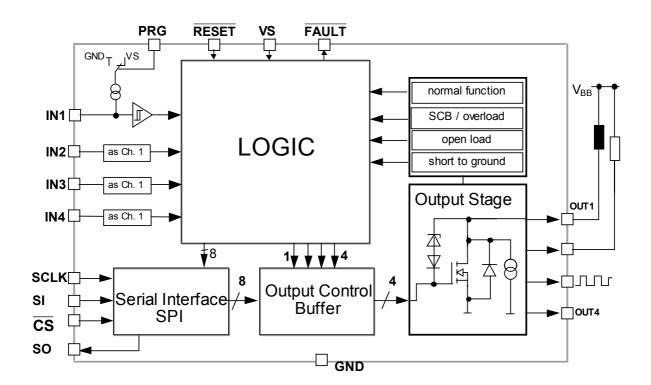

Quad Low-Side Switch in Smart Power Technology (SPT) with a **S**erial **P**eripheral Interface (SPI) and four open drain DMOS output stages. The TLE 6220 GP is protected by embedded protection functions and designed for automotive and industrial applications. The output stages can be controlled direct in parallel for PWM applications (injector coils), or through serial control via the SPI. Therefore the TLE 6220 GP is particularly suitable for engine management and powertrain systems.

**Product Summary**

Output current (all outp. ON equal)

(individually)

Supply voltage

On resistance

Drain source voltage

### Block Diagram

### **Pin Description**

| Pin | Symbol | Function                            |

|-----|--------|-------------------------------------|

| 1   | GND    | Ground                              |

| 2   | IN2    | Input Channel 2                     |

| 3   | OUT1   | Power Output Channel 1              |

| 4   | VS     | Supply Voltage                      |

| 5   | RESET  | Reset                               |

| 6   | CS     | Chip Select                         |

| 7   | PRG    | Program (inputs high or low active) |

| 8   | OUT2   | Power Output Channel 2              |

| 9   | IN1    | Input Channel 1                     |

| 10  | GND    | Ground                              |

| 11  | GND    | Ground                              |

| 12  | IN4    | Input Channel 4                     |

| 13  | OUT3   | Power Output Channel 3              |

| 14  | FAULT  | General Fault Flag                  |

| 15  | SO     | Serial Data Output                  |

| 16  | SCLK   | Serial Clock                        |

| 17  | SI     | Serial Data Input                   |

| 18  | OUT4   | Power Output Channel 4              |

| 19  | IN3    | Input Channel 3                     |

| 20  | GND    | Ground                              |

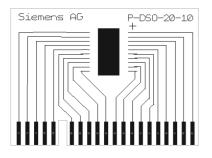

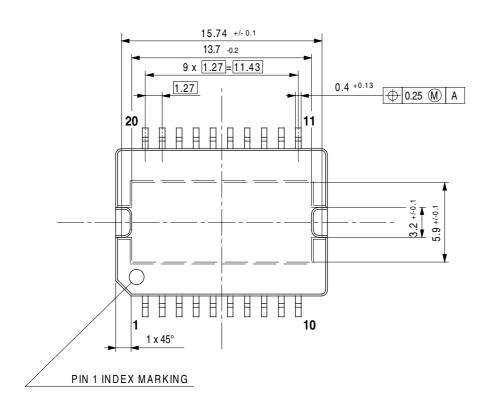

### Pin Configuration (Top view)

| GND   | 1• | 20 | GND   |

|-------|----|----|-------|

| IN2   | 2  | 19 | IN3   |

| OUT1  | 3  | 18 | OUT4  |

| VS    | 4  | 17 | SI    |

| RESET | 5  | 16 | SCLK  |

| CS    | 6  | 15 | SO    |

| PRG   | 7  | 14 | FAULT |

| OUT2  | 8  | 13 | OUT3  |

| IN1   | 9  | 12 | IN4   |

| GND   | 10 | 11 | GND   |

|       |    |    |       |

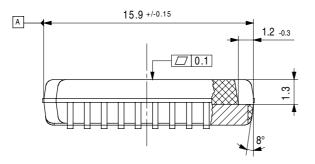

Power SO-20

Heat slug internally connected to ground pins

# Maximum Ratings for $T_j = -40^{\circ}$ C to 150°C

| Parameter                                                                        | Symbol                                | Values                  | Unit |

|----------------------------------------------------------------------------------|---------------------------------------|-------------------------|------|

| Supply Voltage                                                                   | Vs                                    | -0.3 +7                 | V    |

| Continuous Drain Source Voltage (OUT1OUT4)                                       | V <sub>DS</sub>                       | 45                      | V    |

| Input Voltage, All Inputs and Data Lines                                         | V <sub>IN</sub>                       | - 0.3 + 7               | V    |

| Load Dump Protection $V_{\text{Load Dump}} = U_P + U_S$ ; $U_P = 13.5 \text{ V}$ | V <sub>Load Dump</sub> <sup>2</sup> ) |                         | V    |

| With Automotive Injector Valve $R_{\rm L}$ = 14 $\Omega$                         |                                       | 62                      |      |

| $R_{ }^{1}$ = 2 $\Omega$ ; $t_{d}$ = 400ms; IN = low or high                     |                                       |                         |      |

| With $R_{\rm L}$ = 6.8 $\Omega$ ( $I_{\rm D}$ = 2A)                              |                                       | 52                      |      |

| <i>R</i> I=2 Ω; <i>t</i> d=400ms; IN = low or high                               |                                       |                         |      |

| Operating Temperature Range                                                      | Tj                                    | - 40 + 150              | °C   |

| Storage Temperature Range                                                        | T <sub>stg</sub>                      | - 55 + 150              |      |

| Output Current per Channel (see el. characteristics)                             | I <sub>D(lim)</sub>                   | I <sub>D(lim) min</sub> | A    |

| Output Current per Channel @ $T_A = 25^{\circ}C$                                 | I <sub>D</sub>                        | 1                       | A    |

| (All 4 Channels ON; Mounted on PCB ) <sup>3)</sup>                               |                                       |                         |      |

| Output Clamping Energy                                                           | E <sub>AS</sub>                       | 50                      | mJ   |

| / <sub>D</sub> = 1A                                                              |                                       |                         |      |

| Power Dissipation (DC, mounted on PCB) @ $T_A = 25^{\circ}C$                     | P <sub>tot</sub>                      | 3                       | W    |

| Electrostatic Discharge Voltage (human body model)                               | V <sub>ESD</sub>                      | 2000                    | V    |

| according to MIL STD 883D, method 3015.7 and EOS/ESD assn. standard S5.1 - 1993  |                                       |                         |      |

| DIN Humidity Category, DIN 40 040                                                |                                       | E                       |      |

| IEC Climatic Category, DIN IEC 68-1                                              |                                       | 40/150/56               |      |

| Thermal resistance                                                               |                                       |                         | K/W  |

| junction – case (die soldered on the frame)                                      | $R_{ m thJC}$                         | 2                       |      |

| junction - ambient @ min. footprint                                              | <b>R</b> <sub>thJA</sub>              | 50                      |      |

| junction - ambient @ 6 cm <sup>2</sup> cooling area                              |                                       | 38                      |      |

Minimum footprint

PCB with heat pipes, backside 6 cm<sup>2</sup> cooling area

<sup>&</sup>lt;sup>1)</sup>  $R_{l}$ =internal resistance of the load dump test pulse generator LD200 <sup>2)</sup>  $V_{LoadDump}$  is setup without DUT connected to the generator per ISO 7637-1 and DIN 40 839. <sup>3)</sup> Output current rating so long as maximum junction temperature is not exceeded. At  $T_{A}$  = 125 °C the output current has to be calculated using R<sub>thJA</sub> according mounting conditions.

### **Electrical Characteristics**

| Parameter and Conditions                                                                                |                                                  | ool Valu             | Values |        |     |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------|--------|--------|-----|

| $V_{\rm S}$ = 4.5 to 5.5 V ; $T_{\rm j}$ = - 40 °C to + 150 °C ; Reset = H (unless otherwise specified) |                                                  | m                    | in typ | max    |     |

| 1. Power Supply, Reset                                                                                  |                                                  |                      |        |        |     |

| Supply Voltage <sup>4</sup>                                                                             | Vs                                               | 4.5                  |        | 5.5    | V   |

| Supply Current <sup>5</sup>                                                                             | l <sub>s</sub>                                   |                      | 1      | 2      | mA  |

| Minimum Reset Duration                                                                                  | t <sub>Reset</sub> ,                             | min                  | 10     |        | μs  |

| (After a reset all parallel inputs are ORed with data bits)                                             | the SPI                                          |                      |        |        |     |

| 2. Power Outputs                                                                                        |                                                  |                      |        |        |     |

| ON Resistance $V_{\rm S}$ = 5 V; $I_{\rm D}$ = 1 A                                                      | $T_{\rm J} = 25^{\circ} {\rm C}$ $R_{\rm DS(0)}$ | DN)                  | 0.32   | 0.4    | Ω   |

| TJ                                                                                                      | = 150°C                                          |                      |        | 0.7    |     |

| Output Clamping Voltage ou                                                                              | tput OFF V <sub>DS(A</sub>                       | <sub>Z)</sub> 45     | 53     | 60     | V   |

| Current Limit                                                                                           | I <sub>D(lim)</sub>                              | 3                    | 4.5    | 6      | A   |

| Output Leakage Current                                                                                  | $I_{\text{RESET}} = L \qquad I_{\text{D(lkg)}}$  |                      |        | 10     | μA  |

| Turn-On Time $I_D = 1 \text{ A}$ , resist                                                               | stive load $t_{ON}$                              |                      | 5      | 10     | μs  |

| Turn-Off Time $I_{\rm D}$ = 1 A, resist                                                                 | stive load $t_{OFF}$                             |                      | 5      | 10     | μs  |

| 3. Digital Inputs                                                                                       |                                                  |                      |        |        |     |

| Input Low Voltage                                                                                       | V <sub>INL</sub>                                 | - 0.                 | .3     | 1.0    | V   |

| Input High Voltage                                                                                      | V <sub>INH</sub>                                 | 2.0                  |        | VS+0.3 | V   |

| Input Voltage Hysteresis                                                                                | V <sub>INHy</sub>                                | <sub>s</sub> 50      | 100    | 200    | mV  |

| Input Pull Down/Up Current (IN1 IN4)                                                                    | I <sub>IN(14</sub>                               | .) 20                | 50     | 100    | μA  |

| PRG, RESET Pull Up Current                                                                              | I <sub>IN(PR</sub>                               | <sub>G,Res)</sub> 20 | 50     | 100    | μA  |

| Input Pull Down Current (SI, SCLK)                                                                      | I <sub>IN(SI,S</sub>                             | SCLK) 10             | 20     | 50     | μA  |

| Input Pull Up Current ( CS )                                                                            | I <sub>IN(CS)</sub>                              | ) 10                 | 20     | 50     | μA  |

| 4. Digital Outputs (SO, FAULT )                                                                         |                                                  |                      |        |        |     |

| SO High State Output Voltage I <sub>SO</sub>                                                            | н <b>= 2 mA</b> V <sub>SOH</sub>                 | Vs -                 | 0.4    |        | V   |

| SO Low State Output Voltage I <sub>SOL</sub>                                                            | = 2.5 mA V <sub>SOL</sub>                        |                      |        | 0.4    | V   |

| Output Tri-state Leakage Current $\overline{CS}$ = H, $0 \le V_{SO} \le V_S$                            |                                                  | -10                  | 0      | 10     | μA  |

| FAULT Output Low Voltage         IFAULT                                                                 | = 1.6 mA V <sub>FAUI</sub>                       | _TL                  |        | 0.4    | V   |

| Current Limitation; Overload Threshold Curren                                                           | t I <sub>D(lim)</sub>                            | 14 <b>3</b>          | 4.5    | 6      | A   |

|                                                                                                         | -                                                | 4 - 14               | _      | 000    | • • |

$T_{\rm th(sd)}$

$T_{

m hys}$

170

---

---

10

**Overtemperature Shutdown Threshold**

Hysteresis<sup>6</sup>

200

---

°C

Κ

<sup>&</sup>lt;sup>4</sup> For V<sub>S</sub> < 4.5V the power stages are switched according the input signals and data bits or are definitely switched off. This undervoltage reset gets active at V<sub>S</sub> = 3V (typ. value) and is guaranteed by design.

<sup>5</sup> If Reset = L the supply current is reduced to typ. 20μA

<sup>6</sup> This parameter will not be tested but guaranteed by design

### **Electrical Characteristics cont.**

| Parameter and Conditions                                           | Symbol | Values |     |     | Unit |

|--------------------------------------------------------------------|--------|--------|-----|-----|------|

| $V_{s}$ = 4.5 to 5.5 V ; $T_{i}$ = - 40 °C to + 150 °C ; Reset = H |        | min    | typ | max |      |

| (unless otherwise specified)                                       |        |        |     |     |      |

#### 5. Diagnostic Functions

| -                                 |                              |                     |                     |                     |    |

|-----------------------------------|------------------------------|---------------------|---------------------|---------------------|----|

| Open Load Detection Voltage       | V <sub>DS(OL)</sub>          | V <sub>S</sub> -2.5 | V <sub>S</sub> -2   | V <sub>s</sub> -1.3 | V  |

| Output Pull Down Current          | I <sub>PD(OL)</sub>          | 50                  | 90                  | 150                 | μA |

| Fault Delay Time                  | <i>t</i> <sub>d(fault)</sub> | 50                  | 110                 | 200                 | μs |

| Short to Ground Detection Voltage | V <sub>DS(SHG)</sub>         | V <sub>S</sub> -3.3 | V <sub>S</sub> -2.9 | V <sub>S</sub> -2.5 | V  |

| Short to Ground Detection Current | I <sub>SHG</sub>             | -50                 | -100                | -150                | μA |

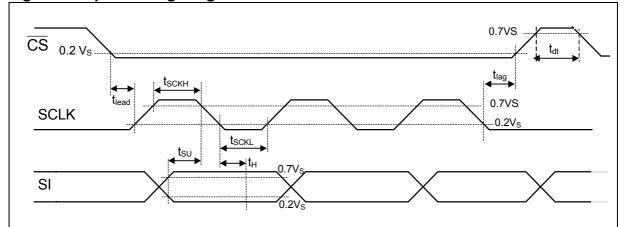

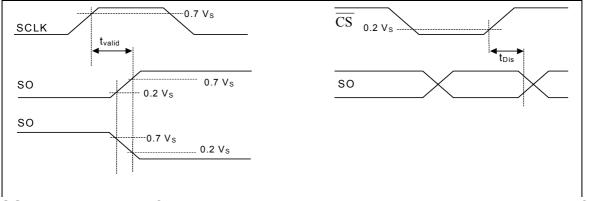

#### 6. SPI-Timing

| Serial Clock Frequency (depending on SO load)                            |                           | DC                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                     | MHz                                                   |

|--------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|                                                                          | $t_{p(SCK)}$              | 200                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

|                                                                          | <b>t</b> <sub>scкн</sub>  | 50                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

|                                                                          | <i>t</i> <sub>SCKL</sub>  | 50                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

|                                                                          |                           | 250                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

| Enable Lag Time (falling edge of CLK to rising edge of $\overline{cs}$ ) |                           | 250                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

| Data Setup Time (required time SI to falling of CLK)                     |                           | 20                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

| Data Hold Time (falling edge of CLK to SI)                               |                           | 20                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

| Disable Time @ C <sub>L</sub> = 50 pF <sup>e</sup>                       |                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                              | 150                                                   | ns                                                    |

| Transfer Delay Time <sup>7</sup>                                         |                           | 200                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       | ns                                                    |

| $(\overline{CS}$ high time between two accesses)                         |                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       |                                                       |

| = 50 pF                                                                  | <i>t</i> <sub>valid</sub> |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                              | 110                                                   | ns                                                    |

|                                                                          |                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                              | 120                                                   |                                                       |

| = 220 pF <sup>8</sup>                                                    |                           |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                              | 150                                                   |                                                       |

|                                                                          | edge of $\overline{CS}$ ) | $t_{p(SCK)}$ $t_{SCKH}$ $t_{SCKL}$ $t_{edge of}$ $t_{lead}$ $t_{edge of}$ $t_{lag}$ $t_{CLK}$ $t_{H}$ $t_{DIS}$ $t_{dt}$ $t_{valid}$ $t_{valid}$ | $\begin{array}{c c c c c c c c c } t_{p(SCK)} & 200 \\ \hline t_{p(SCK)} & 50 \\ \hline t_{SCKL} & 50 \\ \hline t_{SCKL} & 50 \\ \hline t_{sCKL} & 50 \\ \hline t_{lead} & 250 \\ \hline cdge of \overline{CS} ) & t_{lag} & 250 \\ \hline cdge of \overline{CS} ) & t_{lag} & 250 \\ \hline cLK ) & t_{SU} & 20 \\ \hline t_{H} & 20 \\ \hline t_{H} & 20 \\ \hline t_{DIS} & \\ \hline t_{dt} & 200 \\ \hline \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

<sup>&</sup>lt;sup>7</sup> This time is necessary between two write accesses. To get the correct diagnostic information, the transfer delay time has to be extended to the maximum fault delay time  $t_{d(fault)max} = 200 \mu s$ . <sup>8</sup> This parameter will not be tested but guaranteed by design

# **Functional Description**

The TLE 6220 GP is an quad-low-side power switch which provides a serial peripheral interface (SPI) to control the 4 power DMOS switches, as well as diagnostic feedback. The power transistors are protected against short to  $V_{\rm BB}$ , overload, overtemperature and against overvoltage by an active zener clamp.

The diagnostic logic recognises a fault condition which can be read out via the serial diagnostic output (SO).

# **Circuit Description**

#### Power Transistor Protection Functions<sup>9)</sup>

Each of the four output stages has its own zener clamp, which causes a voltage limitation at the power transistor when solenoid loads are switched off. The outputs are provided with a current limitation set to a minimum of 3 A. The continuous current for each channel is 1A (all channels ON; depending on cooling).

Each output is protected by embedded protection functions. In the event of an overload or short to supply, the current is internally limited and the corresponding bit combination is set (early warning). If this operation leads to an overtemperature condition, a second protection level (about 170 °C) will change the output into a low duty cycle PWM (selective thermal shut-down with restart) to prevent critical chip temperatures.

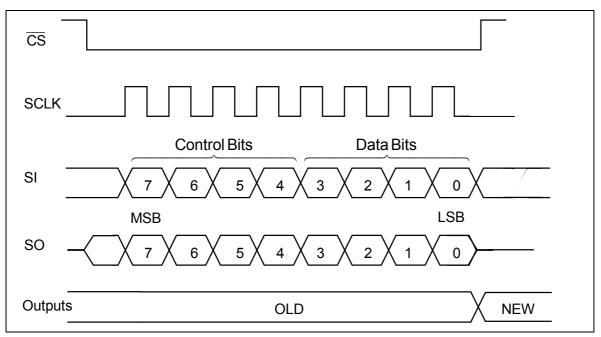

# **SPI Signal Description**

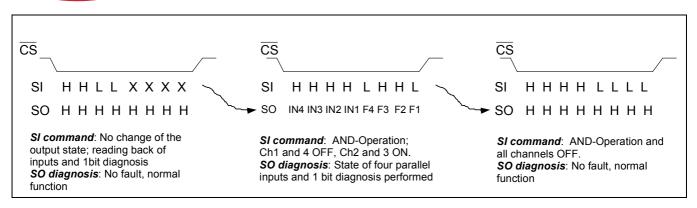

$\overline{CS}$  - Chip Select. The system microcontroller selects the TLE 6220 GP by means of the  $\overline{CS}$  pin. Whenever the pin is in a logic low state, data can be transferred from the  $\mu C$  and vice versa.

| <b>CS</b> High to Low transition: | <ul> <li>Diagnostic status information is transferred from the power outputs into the shift register.</li> <li>Serial input data can be clocked in from then on.</li> <li>SO changes from high impedance state to logic high or low state corresponding to the SO bits.</li> </ul> |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS Low to High transition:        | <ul> <li>Transfer of SI bits from shift register into output buffers</li> <li>Reset of diagnosis register.</li> </ul>                                                                                                                                                              |

To avoid any false clocking the serial clock input pin SCLK should be logic low state during high to low transition of  $\overline{CS}$ . When  $\overline{CS}$  is in a logic high state, any signals at the SCLK and SI pins are ignored and SO is forced into a high impedance state.

<sup>&</sup>lt;sup>9</sup>)The integrated protection functions prevent an IC destruction under fault conditions and may not be used in normal operation or permanently.

**SCLK** - Serial Clock. The system clock pin clocks the internal shift register of the TLE 6220 GP. The serial input (SI) accepts data into the input shift register on the falling edge of SCLK while the serial output (SO) shifts diagnostic information out of the shift register on the rising edge of serial clock. It is essential that the SCLK pin is in a logic low state whenever chip select  $\overline{CS}$  makes any transition.

**SI** - Serial Input. Serial data bits are shifted in at this pin, the most significant bit first. SI information is read in on the falling edge of SCLK. Input data is latched in the shift register and then transferred to the control buffer of the output stages.

The input data consists of one byte, made up of four control bits and four data bits. The control word is used to program the device, to operate it in a certain mode as well as providing diagnostic information (see page 11). The four data bits contain the input information for the four channels, and are high active.

**SO** - Serial Output. Diagnostic data bits are shifted out serially at this pin, the most significant bit first. SO is in a high impedance state until the  $\overline{CS}$  pin goes to a logic low state. New diagnostic data will appear at the SO pin following the rising edge of SCLK.

**RESET** - Reset pin. If the reset pin is in a logic low state, it clears the SPI shift register and switches all outputs OFF. An internal pull-up structure is provided on chip. As long as the reset pin is low the device is in low quiescent current mode and the supply current is reduced to typ.  $20\mu$ A.

# Output Stage Control

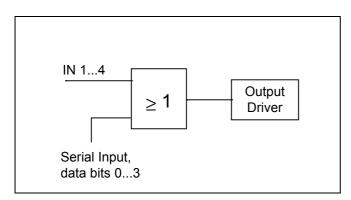

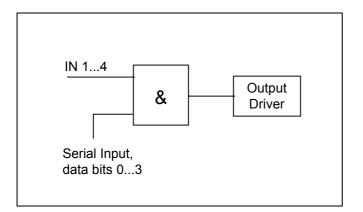

The four outputs of the TLE 6220 GP can either be controlled in parallel (IN1...IN4), or via the Serial Peripheral Interface (SPI).

#### Parallel Control

A Boolean operation (either AND or OR) is performed on each of the parallel inputs and respective SPI data bits, in order to determine the states of the respective outputs. The type of Boolean operation performed is programmed via the serial interface.

The parallel inputs are high or low active depending on the PRG pin. If the parallel input pins are not connected (independent of high or low activity) it is guaranteed that the outputs 1 to 4 are switched OFF. PRG pin itself is internally pulled up when it is not connected.

**PRG** - Program pin. PRG = High ( $V_S$ ): Parallel inputs Channel 1 to 4 are high active PRG = Low (GND): Parallel inputs Channel 1 to 4 are low active.

#### Serial Control of the Outputs: SPI protocol

Each output is independently controlled by an output latch and a common reset line, which disables all four outputs. The Serial Input (SI) is read on the falling edge of the serial clock. A logic high input 'data bit' turns the respective output channel ON, a logic low 'data bit' turns it OFF.  $\overline{CS}$  must be low whilst shifting all the serial data into the device. A low-to-high transition of  $\overline{CS}$  transfers the serial data input bits to the output control buffer.

As mentioned above, the serial input byte consists of a 4 bit control word and a 4 bit data word. Via the control word, the specific mode of the device is programmable.

CCCC DDDD Control Bits Data Bits

Five specific control words are recognised, having the following functions:

| No. | Serial Input Byte | Function                                                       |

|-----|-------------------|----------------------------------------------------------------|

| 1   | LLLL XXXX         | Only 'Full Diagnosis' performed. No change to output states.   |

| 2   | HHLL XXXX         | State of four parallel inputs and '1-bit Diagnosis' outputted. |

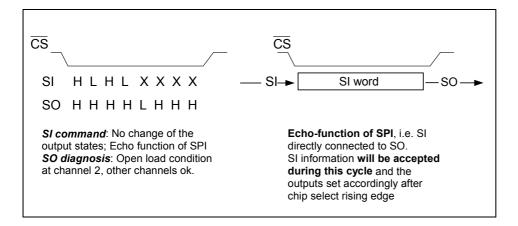

| 3   | HLHL XXXX         | Echo-function of SPI; SI direct connected to SO                |

| 4   | LLHH DDDD         | IN14 and serial data bits 'OR'ed. 'Full Diagnosis' performed.  |

| 5   | HHHH DDDD         | IN14 and serial data bits 'AND'ed. 'Full Diagnosis' performed. |

Note: 'X' means 'don't care', because this bit will be ignored 'D' represents the data bit, either being H (=ON) or L (=OFF)

#### 1. LLLL XXXX - Diagnosis only

By clocking in this control byte, it is possible to get pure diagnostic information (two bits per channel) in accordance with Figure 1 (page 11). The data bits are ignored, so that the state of the outputs are not influenced. This command is only active once unless the next control command is again "Diagnosis only".

#### 2. HHLL XXXX - Reading back of input, and '1-bit Diagnosis'

If the TLE 6220 GP is used as bare die in a hybrid application, it is necessary to know if proper connections exist between the  $\mu$ C-port and parallel inputs. By entering 'HHLL' as the control word, the first four bits of the SO give the state of the parallel inputs, depending on the  $\mu$ C signals. By comparing the four IN-bits with the corresponding  $\mu$ C-port signal, the necessary connection between the  $\mu$ C and the TLE 6220 can be verified - i.e. 'read back of the inputs'. The second 4-bit word fed out at the serial output contains '1-bit' fault information of the outputs (H = no fault, L = fault). In the expression given below for the output byte, 'FX' is the fault bit for channel X.

IN4 IN3 IN2 IN1 F4 F3 F2 F1 : Serial Output byte

### 3. HLHL XXXX - Echo-function of SPI

To check the proper function of the serial interface the TLE 6220 GP provides a "SPI Echo Function". By entering HLHL as control word, SI and SO are connected during the next  $\overline{CS}$  period. By comparing the bits clocked in with the serial output bits, the proper function of the SPI interface can be verified. This internal loop is only closed once (for one  $\overline{CS}$  period).

4. LLHH DDDD - OR operation, and 'full diagnosis'

With LLHH as the control word, each of the input signals IN1...IN4 are 'OR'ed with the corresponding data bits (DDDD).

This OR operation enables the serial interface to switch the channel ON, even though the corresponding parallel input might be in the off state.

#### **SPI Priority for ON-State**

Also parallel control of the outputs is possible without an SPI input.

The OR-function is the default Boolean operation if the device restarts after a Reset, or when the supply voltage is switched on for the first time.

If the OR operation is programmed it is latched until it is overwritten by the AND operation.

#### 5. HHHH DDDD - AND operation, and 'full diagnosis'

With HHHH as the control word, each of the input signals IN1...IN4 are 'AND'ed with the corresponding data bits (DDDD).

The AND operation implies that the output can be switched off by the SPI data bit input, even if the corresponding parallel input is in the ON state.

#### **SPI Priority for OFF-state**

This also implies that the serial input data bit can only switch the output channel ON if the corresponding parallel input is in the ON state.

If the AND operation is programmed it is latched until it is overwritten by the OR operation.

#### Control words beside No. 1-5

All control words except those for Diag Only, Read Back of Inputs, SPI echo, will be accepted as an OR or an AND command with valid data bits depending on the boolean operation which was programmed before.

#### Example 1:

LLHH HLLH: OR operation between parallel inputs and data bits, i.e channel 1 and 4 will be switched on.

#### The next command is now: LHHH HHLH

LHHH as command word has no special meaning but it will be accepted as an OR operation and the data bits will be ORed with the inputs and the outputs 1,3 and 4 will be switched on. See above: 'If the OR operation is programmed it is latched until it is overwritten by the AND operation.'

#### Example 2:

HHHH LLHL means: Data bits will be ANDed with the parallel inputs and the outputs switch accordingly. Then **HLLH HHLH** is clocked in: AND was latched by the command before and is now valid again by using the HLLH command word. So the data bits will be accepted and again ANDed with the parallel input signals.

See above: 'If the AND operation is programmed it is latched until it is overwritten by the OR operation.'

# Diagnostics

**FAULT** - Fault pin. There is a general fault pin (open drain) which shows a high to low transition as soon as an error occurs for any one of the four channels. This fault indication can be used to generate a  $\mu$ C interrupt. Therefore a 'diagnosis' interrupt routine need only be called after this fault indication. This saves processor time compared to a cyclic reading of the SO information.

As soon as a fault occurs, the fault information is latched into the diagnosis register. A new error will over-write the old error report. Serial data out pin (SO) is in a high impedance state when  $\overline{CS}$  is high. If  $\overline{CS}$  receives a LOW signal, all diagnosis bits can be shifted out serially. The rising edge of  $\overline{CS}$  will reset all error registers.

### Full Diagnosis

For full diagnosis there are two diagnostic bits per channel configured as shown in Figure 1.

| Diagnostic Serial OUT (SO)                                                                                                                       |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $ \underbrace{7 \times 6 \times 5 \times 4 \times 3 \times 2 \times 1 \times 0 \times 1}_{\text{A}} $                                            |  |

| Ch.4 Ch.3 Ch.2 Ch.1                                                                                                                              |  |

| <ul> <li>HH Normal function</li> <li>HL Overload, Shorted Load or Overtemperature</li> <li>LH Open Load</li> <li>LL Shorted to Ground</li> </ul> |  |

#### Figure 1: Two bits per channel diagnostic feedback

**Normal function:** The bit combination **HH** indicates that there is no fault condition, i.e. normal function.

**Overload, Short Circuit to Battery (SCB) or Overtemperature: HL** is set when the current limitation gets active, i.e. there is a overload, short to supply or overtemperature condition.

**Open load:** An open load condition is detected when the drain voltage decreases below 3 V (typ.). **LH** bit combination is set.

**Short Circuit to GND:** If a drain to ground short circuit exists and the drain to ground current exceeds 100  $\mu$ A, short to ground is detected and the **LL** bit combination is set.

A definite distinction between open load and short to ground is guaranteed by design.

The standard way of obtaining diagnostic information is as follows:

Clock in serial information into SI pin and wait approximately 150  $\mu$ s to allow the outputs to settle. Clock in the identical serial information once again - during this process the data coming out at SO contains the bit combinations representing the diagnosis conditions as described in Figure 1.

### **Timing Diagrams**

#### Figure 2: Serial Interface Figure 3: Input Timing Diagram

### Figure 4:

### SO Valid Time Waveforms

Enable and Disable Time Waveforms

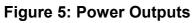

**Application Circuit**

# **Typical electrical Characteristics**

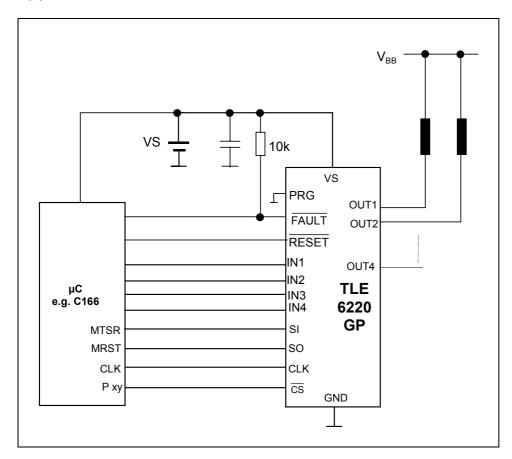

# **Drain-Source on-resistance**

$R_{DS(ON)} = f(T_j)$ ;  $V_s = 5V$

Figure 6 : Typical ON Resistance versus Junction-Temperature Channel 1-4

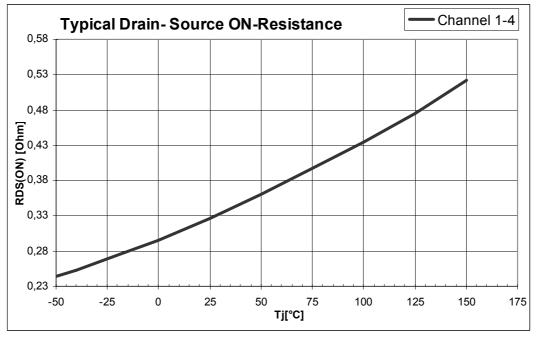

# **Output Clamping Voltage**

$V_{DS(AZ)} = f(T_j)$ ;  $V_s = 5V$

Figure 7 : Typical Clamp Voltage versus Junction-Temperature Channel 1-4

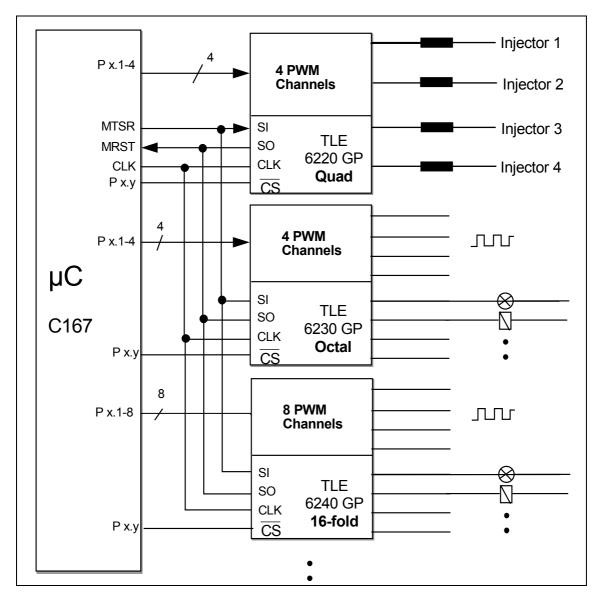

# **Parallel SPI Configuration**

#### **Engine Management Application**

TLE 6230 GP in combination with TLE 6240 GP (16-fold switch) for relays and general purpose loads and TLE 6220 GP (quad switch) to drive the injector valves. This arrangement covers the numerous loads to be driven in a modern Engine Management/Powertrain system. From 28 channels in sum 16 can be controlled direct in parallel for PWM applications.

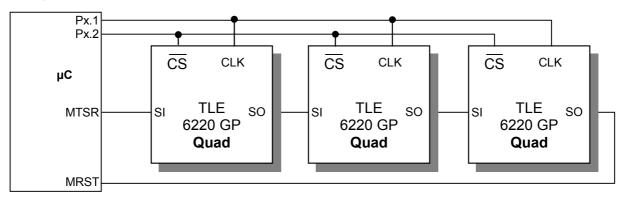

# **Daisy Chain Application TLE 6220 GP**

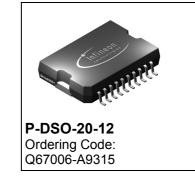

# Package and Ordering Code

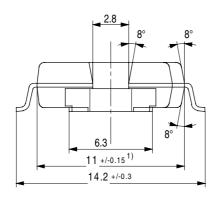

#### (all dimensions in mm)

| P - DSO - 20 - 12 | Ordering Code |

|-------------------|---------------|

| TLE 6220 GP       | Q67006-A9315  |

Published by Infineon Technologies AG, Bereichs Kommunikation St.-Martin-Strasse 76, D-81541 München © Infineon Technologies AG 1999 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.